#### DEPARTMENT OF INFORMATION TECHNOLOGY AND ELECTRICAL ENGINEERING

Fall Semester 2022

## Design and Validation of a Combined Power Tracer and Sensor Emulator for the Evaluation of Embedded Hardware/Software System Designs

Master Thesis

Nando Galliard gnando@protonmail.ch

March 2023

| Supervisors: | Christian Vogt, christian.vogt@pbl.ee.ethz.ch          |

|--------------|--------------------------------------------------------|

|              | Federico Villani, federico.villani@pbl.ee.ethz.ch      |

| Professor:   | Prof. Dr. Florian Dörfler, doerfler@control.ee.ethz.ch |

## Acknowledgements

The author would like to commence this report by expressing gratitude to numerous individuals who provided invaluable assistance throughout the course of this master's thesis. Sincere appreciation is extended to the two supervisors, Dr. Christian Vogt and Federico Villani, whose guidance and mentorship were instrumental in the project's success. Furthermore, the author is grateful to Elio Reinschmidt, Silvano Cortesi, and Gian Köppel, whose expertise in embedded IoT design and FPGA programming significantly contributed to the research.

## Abstract

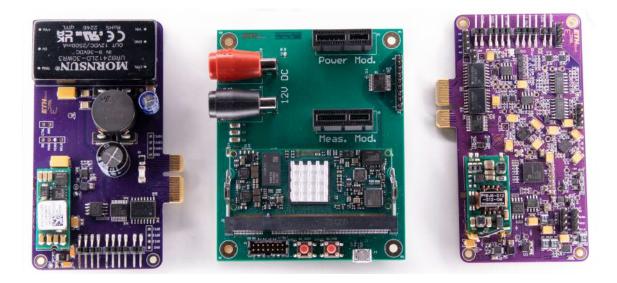

This report presents the development of a novel hardware in the loop testbed for embedded devices, capable of measuring a broad range of currents and voltages, providing power delivery, and enabling simultaneous stimulation and data recording for the device under test. The modular testbed comprises three primary components: the power profiler module, the power delivery module, and the data interposer module. By achieving a current measurement range of 210 dB and offering 20 W of power delivery to the DUT, this HIL testbed demonstrates a comprehensive solution for testing low-power devices and those requiring high inrush current, such as FPGAs. The modular design allows for easy expansion and adaptation to meet the evolving needs of modern embedded systems and serves as a foundation for future work and development in the field.

## Declaration of Originality

I hereby confirm that I am the sole author of the written work here enclosed and that I have compiled it in my own words. Parts excepted are corrections of form and content by the supervisor. For a detailed version of the declaration of originality, please refer to Appendix C

Nando Galliard, Zurich, March 2023

## Contents

| Li | st of                 | Acronyms                                                   | xi |

|----|-----------------------|------------------------------------------------------------|----|

| 1. | $\operatorname{Intr}$ | oduction                                                   | 1  |

| 2. | Rela                  | ted Work                                                   | 3  |

|    | 2.1.                  | Power Profiling Methods                                    | 4  |

|    |                       | 2.1.1. Dual shunt resistor stage                           | 4  |

|    |                       | 2.1.2. Highly dynamic power consumption measurement        | 4  |

|    |                       | 2.1.3. Shunt Resistor in the loop                          | 4  |

|    |                       | 2.1.4. Hal Effect Current Sensing                          | 5  |

|    |                       | 2.1.5. Mobile Power Logger for Prototyping IoT Devices     | 5  |

|    | 2.2.                  | Sensor Emulation and Injection                             | 6  |

|    |                       | 2.2.1. Automation in HIL Units Development and Integration | 6  |

|    | 2.3.                  | Industry Devices                                           | 6  |

| 3. | Fun                   | lamentals                                                  | 8  |

|    | 3.1.                  | Sensing Elements for Current Measurement                   | 8  |

|    |                       | 3.1.1. Current measurement using Shunt Resistor            | 8  |

|    |                       | 3.1.2. Measurement using Hall Effect sensor                | 9  |

|    |                       | 3.1.3. Direct Current Resistance                           | 9  |

|    | 3.2.                  | Hysteric Circuit                                           | 10 |

|    | 3.3.                  | ADC Precision and Resolution                               | 11 |

|    |                       | 3.3.1. Noise in Measurements                               | 12 |

|    |                       | 3.3.2. Effective number of bits                            | 13 |

| 4. | Des                   | gn Implementation Of Modules                               | 14 |

|    |                       |                                                            | 14 |

|    |                       | Power Profiler Module                                      | 14 |

|    |                       | 4.2.1. ADC AD7134                                          | 16 |

|    |                       | 4.2.2. Instrumentation Amplyfier                           | 16 |

#### Contents

|    |                | 4.2.3. Driver Input to ADC                                                               | 17              |

|----|----------------|------------------------------------------------------------------------------------------|-----------------|

|    |                |                                                                                          | 18              |

|    |                | 4.2.5. Hysteresis Cascade                                                                | 19              |

|    |                | 4.2.6. High Power Mode for Current Measurement                                           | 21              |

|    |                | 4.2.7. Power Planes                                                                      | 21              |

|    |                | 4.2.8. Isolation                                                                         | 22              |

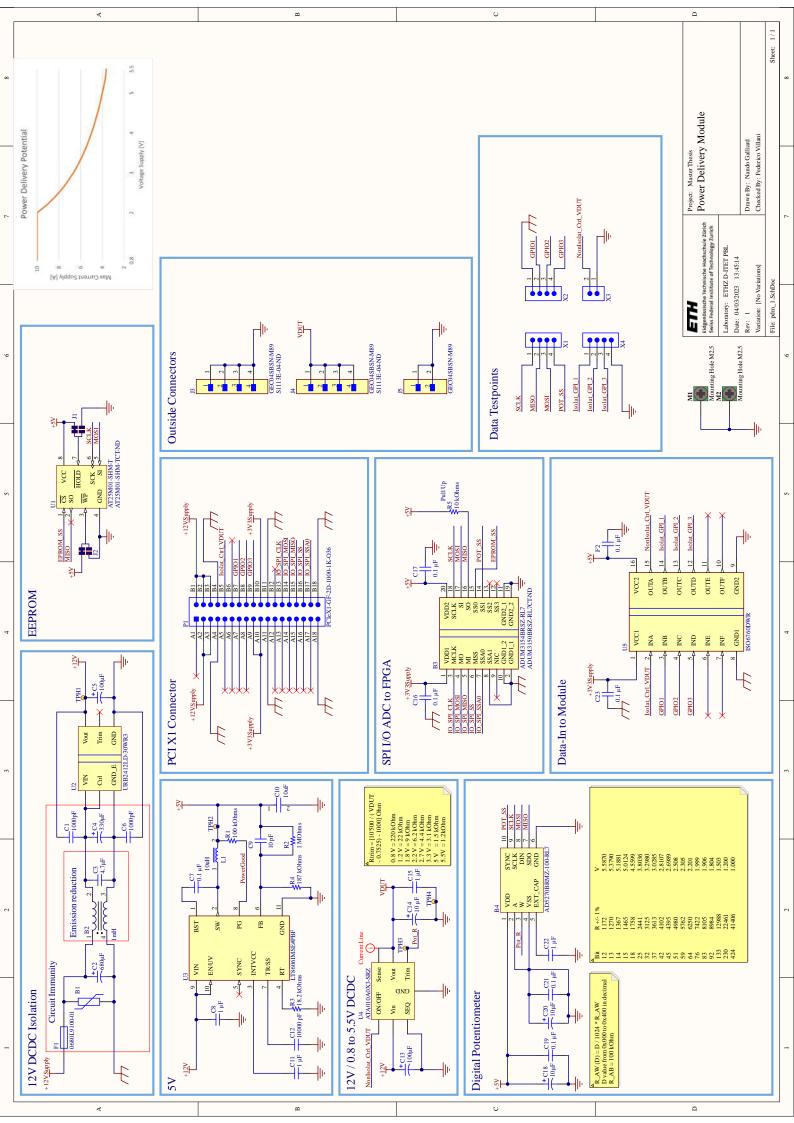

|    | 4.3.           | Power Delivery Module                                                                    | $23^{}$         |

|    | 1.0.           | 4.3.1. DC-DC Power Delivery to DUT                                                       | $\frac{-0}{23}$ |

|    |                | 4.3.2. Isolation                                                                         | 24              |

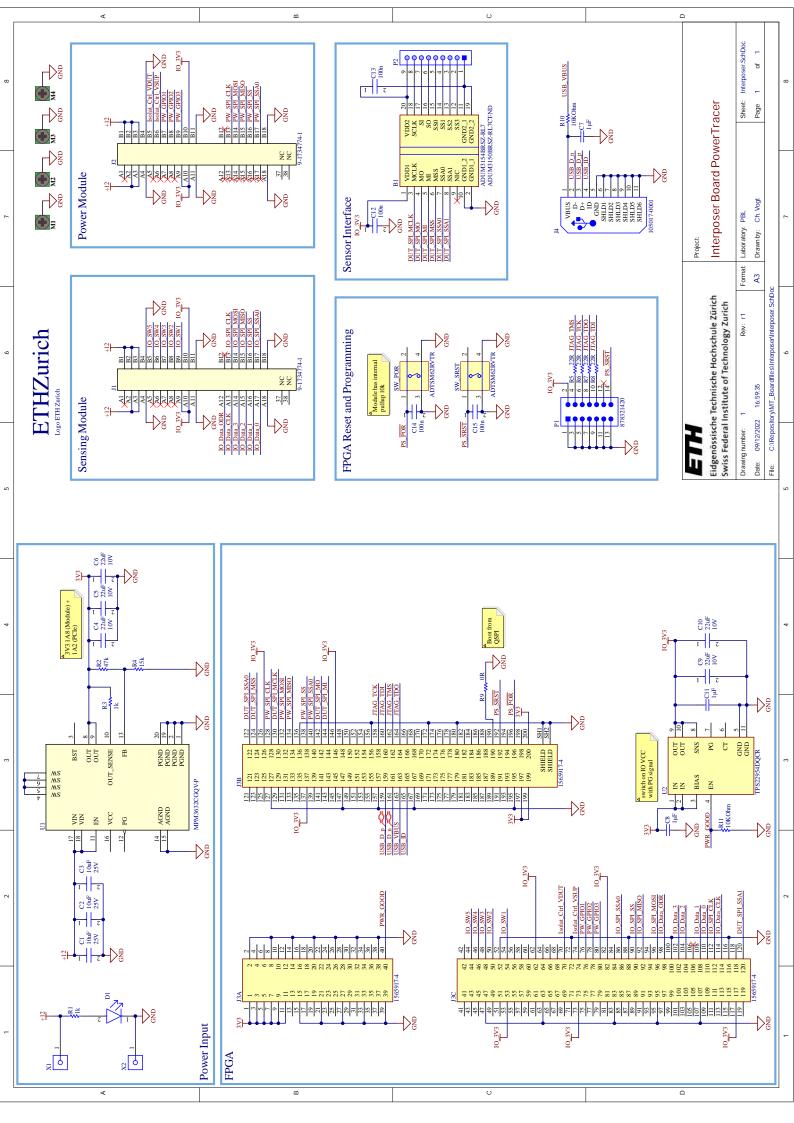

|    | 44             | Data Interposer Module                                                                   | 25              |

|    |                | Mars ZX2 Module                                                                          | $\frac{1}{26}$  |

|    |                |                                                                                          |                 |

| 5. |                |                                                                                          | 27              |

|    | 5.1.           | ADC RTL Architecture                                                                     | 28              |

| 6. | $\mathbf{Sim}$ | ulation of Analog Circuit                                                                | 29              |

|    | 6.1.           | Simulation Software                                                                      | 29              |

|    | 6.2.           | Simulation Settings                                                                      | 29              |

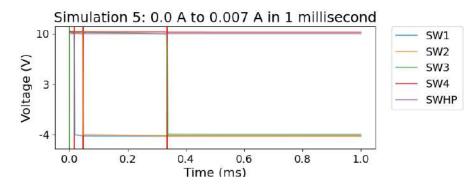

|    |                | 6.2.1. Rising Current 0A to 7 mA                                                         | 30              |

|    |                | 6.2.2. Rising Current 0A to 7 mA $\simeq$ Bigger Resistor at MOSFET Gate $% A_{\rm e}$ . | 31              |

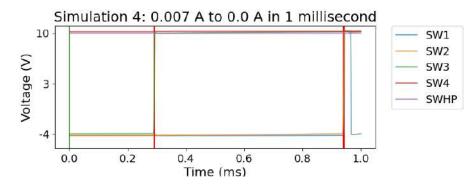

|    |                | 6.2.3. Falling 7mA to 0A                                                                 | 31              |

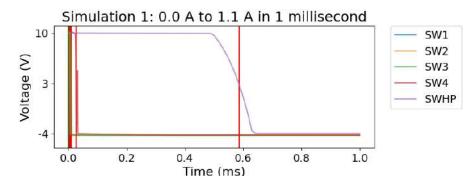

|    |                | 6.2.4. Rising Current 0A to 1.1A                                                         | 32              |

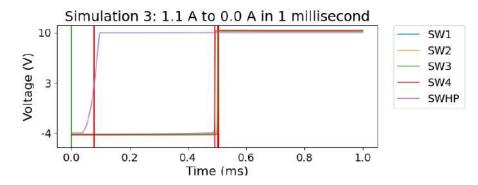

|    |                | 6.2.5. Falling Current 1.1A to 0A                                                        | 32              |

|    |                | 6.2.6. Switching time of Cascade Steps                                                   | 33              |

| 7. | Exp            | erimental Setup                                                                          | <b>34</b>       |

|    | -              | Definition Of Ground Truth                                                               | 34              |

|    |                | 7.1.1. Measurement Uncertainties                                                         | 35              |

|    | 7.2.           | Measurement Setup PPM Current to Measure Switch Points                                   | 37              |

|    |                | 7.2.1. Measurement Setup PPM Current Pulse to Measure Switch Points                      | 37              |

|    | 7.3.           | Measurement Setup PPM Current ADC Output                                                 | 38              |

|    |                | Measurement Setup PPM Voltage Output                                                     | 39              |

|    | 7.5.           | * 0 *                                                                                    | 40              |

| 8  | Res            | ults                                                                                     | 41              |

| 0. | 8.1.           | Data Calibration                                                                         | 41              |

|    | 0              | Results PPM Current to Measure Switch Points                                             | 42              |

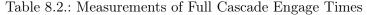

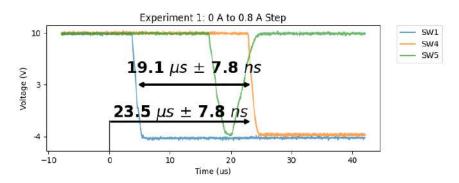

|    | 0.2.           | 8.2.1. Results PPM Step Current to Measure Switch Points                                 | 44              |

|    | 8.3.           | Results PPM Current Data from ADC                                                        | 45              |

|    | 8.4.           | Results PPM Voltage Data from ADC                                                        | 47              |

|    | 8.5.           | Results PDM VDUT Output                                                                  | 48              |

|    |                | -                                                                                        | 10              |

| 9. |                |                                                                                          | <b>49</b>       |

|    | 9.1.           | Power Profiler Module                                                                    | 49              |

#### Contents

| 9.2. Power Delivery Module    | 51        |

|-------------------------------|-----------|

| 9.3. Data Interjection        | 52        |

| 9.4. Summary Table            | 52        |

| 10.Conclusion                 | <b>53</b> |

| 10.1. Future Work             | 54        |

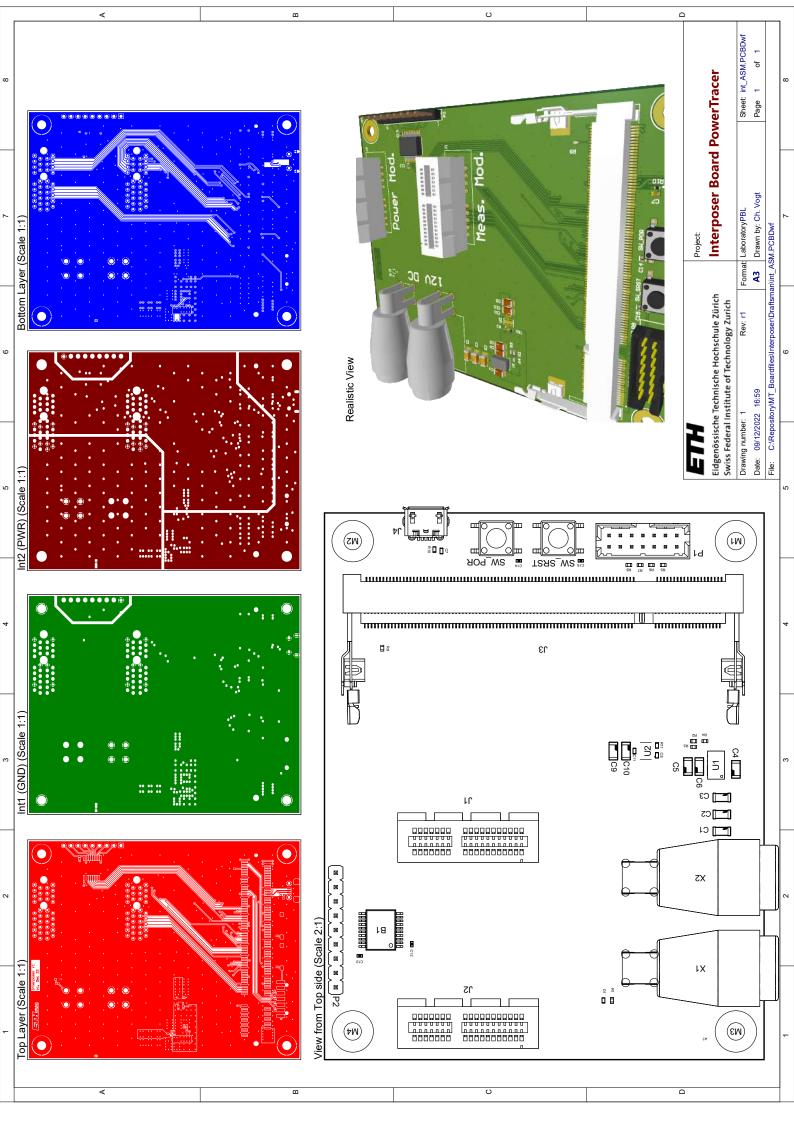

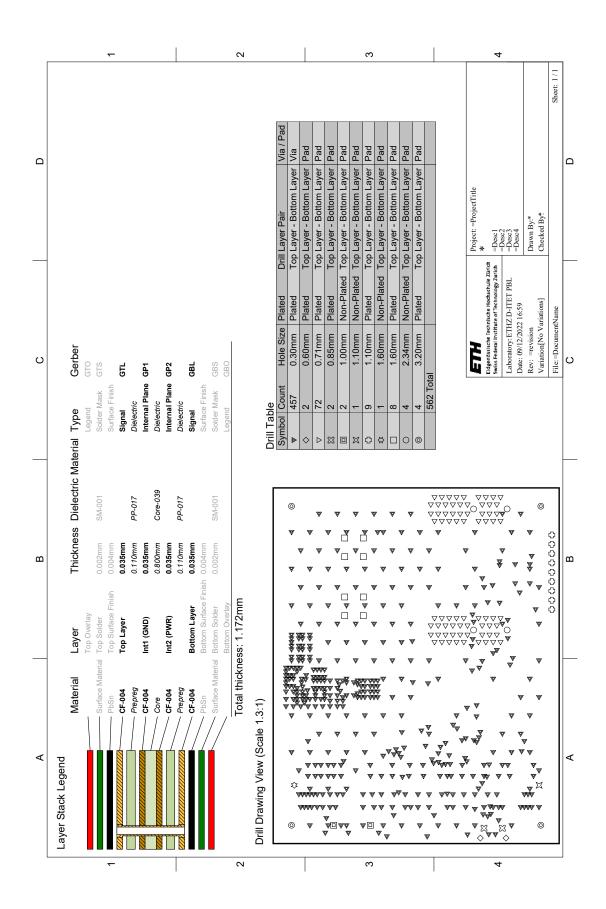

| A. System Setup Appendix      | 55        |

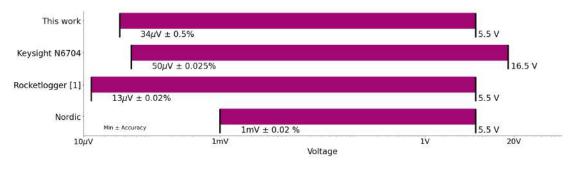

| A.1. Python GUI and Driver    | 55        |

| A.2. Programming of AD7134    | 55        |

| B. Task Description           | <b>58</b> |

| C. Declaration of Originality | 64        |

| D. File Structure             | 65        |

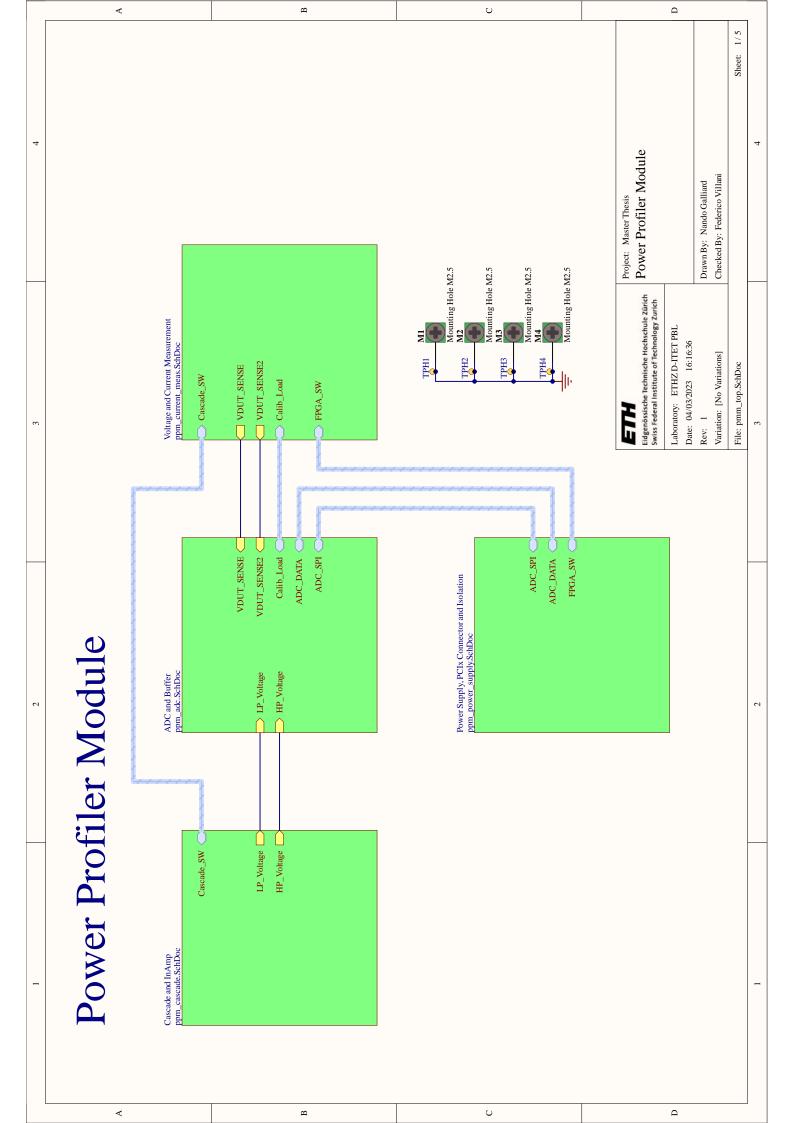

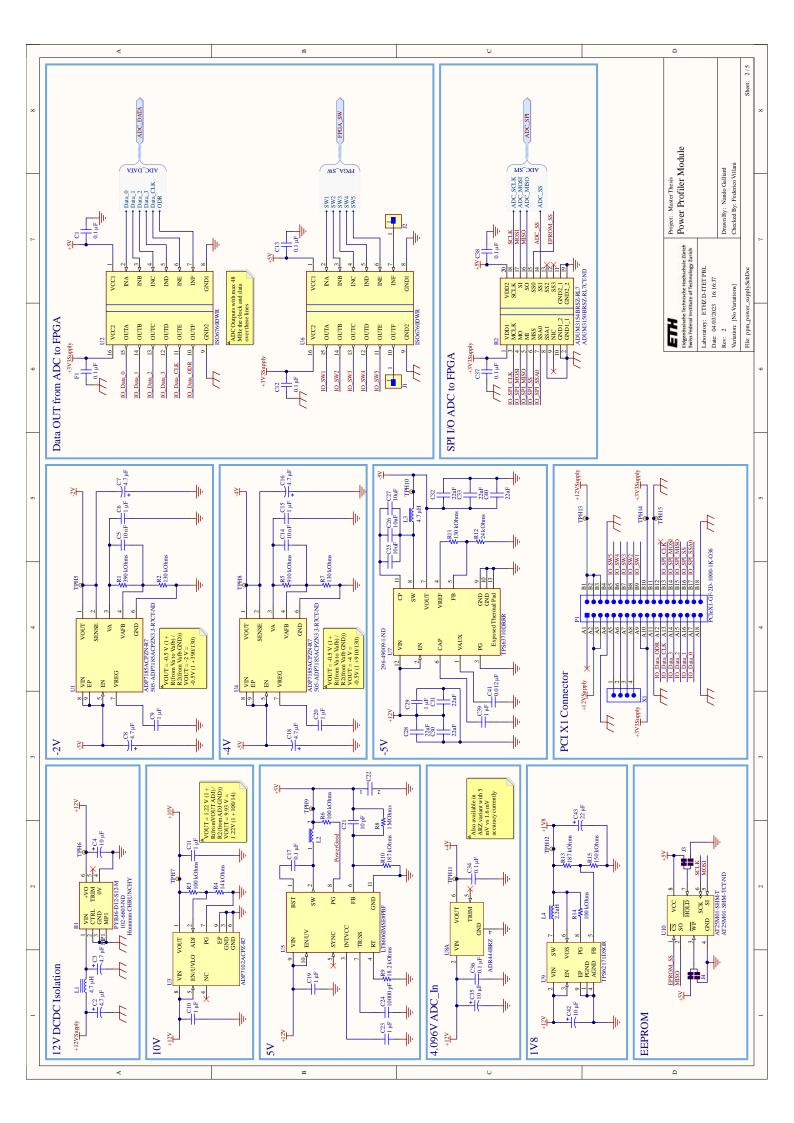

| E. PPM Schematic              | 66        |

| F. PDM Schematic              | 71        |

| G. DIM Schematic              | 72        |

| Glossary                      | 76        |

# List of Figures

| 3.1.  | Simple Schematic of a DRC Circuit from [1]                               | 9  |

|-------|--------------------------------------------------------------------------|----|

| 3.2.  | Hysteric Circuit                                                         | 11 |

| 3.3.  | Voltag Plot for Hysteric Circuit                                         | 11 |

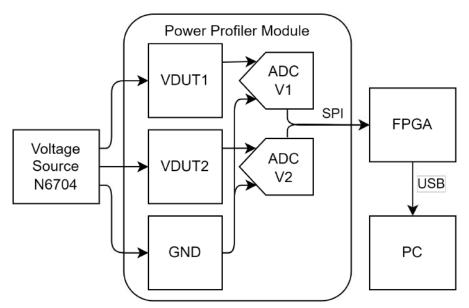

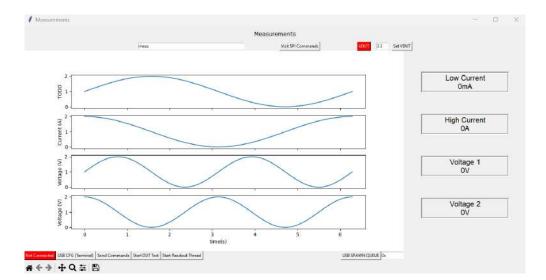

| 4.1.  | High Level Block diagram of PPM Data and Measurement Lines $\ .\ .\ .$ . | 15 |

| 4.2.  | Power Profiler Module                                                    | 15 |

| 4.3.  | Diamond Plot of AD8421ARZ under design specifications                    | 17 |

| 4.4.  | N&D Summary                                                              | 17 |

| 4.5.  | Contributions to System THD                                              | 17 |

| 4.6.  | Variable Shunt Resistance Schematic                                      | 18 |

| 4.7.  | Hysteresis Cascade Circuit Schematic                                     | 19 |

| 4.8.  | Cascade Components                                                       | 20 |

| 4.9.  | High Power Mode for Current Measurement                                  | 21 |

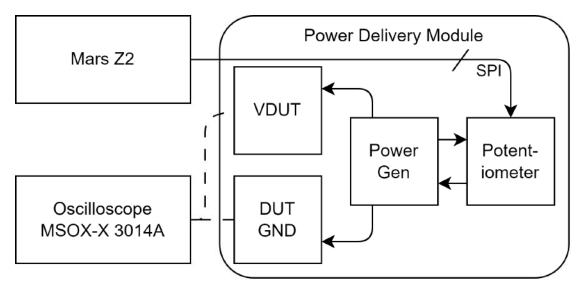

| 4.10. | Block Diagram of PDM                                                     | 23 |

| 4.11. | High-Level Block Diagram of PDM Data and Power Delivery Lines            | 24 |

| 4.12. | Measurement Setup data exchange with DUT                                 | 25 |

| 4.13. | Data Interposer Module                                                   | 26 |

| 5.1.  | Real Time Datastream from ADC to PC                                      | 27 |

| 5.2.  | State Machine of ADC RTL Module                                          | 28 |

| 5.3.  | 128-bit AXI Stream Package                                               | 28 |

| 6.1.  | Rising and Falling Currents                                              | 30 |

| 6.2.  | Step Function Currents                                                   | 30 |

| 6.3.  | Step Current Through Shunt at 3 A                                        | 33 |

| 6.4.  | Step Current Through Shunt at 800 mA $\ldots$                            | 33 |

| 7.1.  | Measurement Setup for Cascade Measurements Graphic                       | 37 |

| 7.2.  | Measurement Setup for Cascade Measurements Picture                       | 38 |

| 7.3.  | Measurement Setup for Voltage Measurements of PPM                        | 39 |

|       |                                                                          |    |

#### List of Figures

| 7.4.  | Measurement Setup Power Generator DUT         |

|-------|-----------------------------------------------|

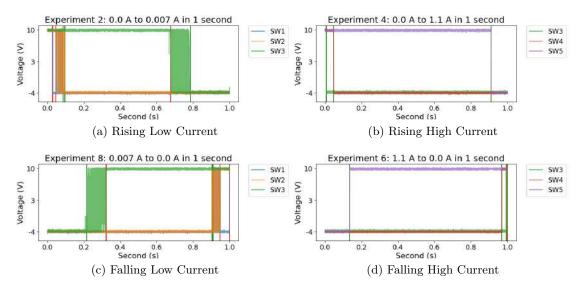

| 8.1.  | PPM Switching Measurements 43                 |

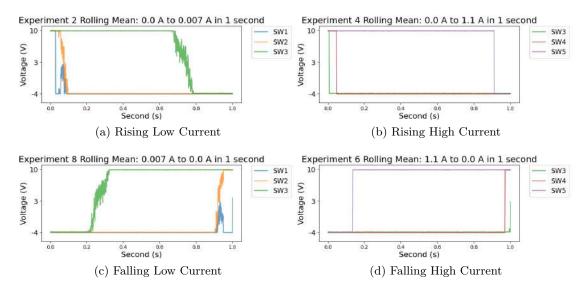

| 8.2.  | PPM Switching Measurements Rolling Average 43 |

| 8.3.  | Rising Low Current Pulse                      |

| 8.4.  | Rising High Current Pulse                     |

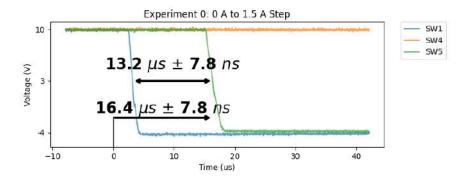

| 8.5.  | Caption                                       |

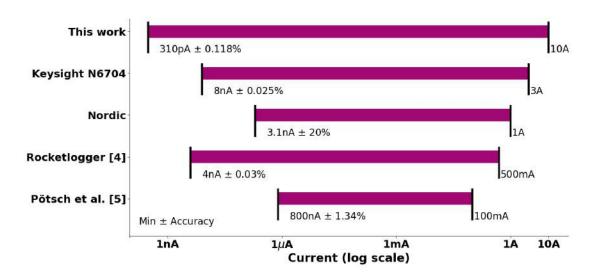

| 9.1.  | Current Ranges State of the Art               |

| 9.2.  | Voltage Ranges State of the Art               |

| 10.1. | Full Prototype with PPM, PDM and Interposer   |

| A.1.  | Python GUI to interact with the testbench     |

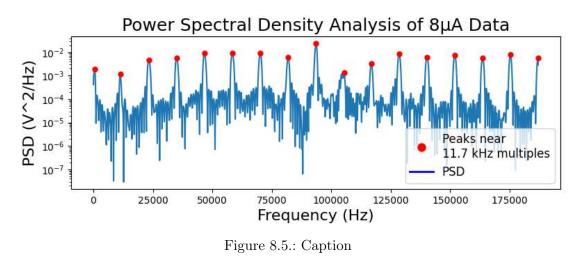

# List of Tables

| 2.1.                                                               | Summary of related industry devices                                                                                                                                     |

|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                    | Variable Shunt Resistor Resistances18Current Density on PPM22                                                                                                           |

|                                                                    | Devices used for Measurements    35      Single Measurement Errors    35                                                                                                |

| <ol> <li>8.2.</li> <li>8.3.</li> <li>8.4.</li> <li>8.5.</li> </ol> | Measurements of Switching Points of Cascade42PPM Full Cascade Rise Times44PPM ADC Low Current Table46PPM ADC Voltage 1 Table47PPM ADC Voltage 2 Table48PDM VDUT Table48 |

| 9.1.                                                               | Summary of Keypoints of this Work versus Related Work                                                                                                                   |

| A.1.                                                               | Programming of the Register Bank                                                                                                                                        |

# List of Acronyms

| ADC                               |

|-----------------------------------|

| ADS advanced design systems       |

| CRC                               |

| DIMdata interposer module         |

| DMA direct memory access          |

| DUT device under test             |

| EDA electronic design automation  |

| EMC electromagnetic compatibility |

| ENOB effective number of bits     |

| ESD electro static discharge      |

| FIFO first in first out           |

| FPGA                              |

| HIL                               |

| InAmp instrumentation amplifier   |

| IP                                |

|                                   |

LDO  $\hdots$  . . . . . . Low-dropout regulator

#### List of Acronyms

MOSFET . . . . metal oxide silicon field effect transistor

- ODR .....output data rate

- $OpAmp \ \ . \ . \ . \ . \ operational \ amplifier$

PDM .... power delivery module

PL . . . . . . . . . programmable logic

${\rm PPM} \quad . \ . \ . \ . \ . \ power \ profiler \ module$

PS . . . . . . . . . processing system

PSD . . . . . . . . . power spectral density

RF . . . . . . . . . radio frequency

RTL . . . . . . . . register transfer level

- RTOS  $\ldots$  . . . . . . real time operating system

- SINAD . . . . . . signal to noise and distortion

SoC . . . . . . . . system on chip

SPI . . . . . . . . . serial peripheral interface

THD . . . . . . . . . . total harmonic distortion

#### l Chapter

### Introduction

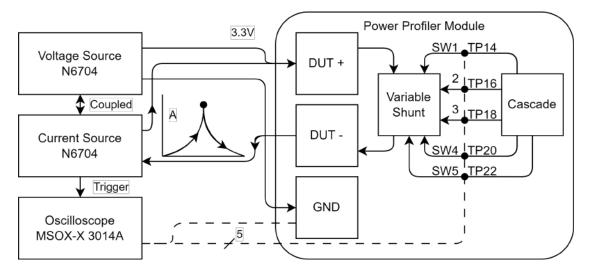

For any scientific report, the reproducibility of an experiment is one of the critical pillars on which the scientific community stands. In the field of embedded devices, it has always been a challenging endeavour to reproduce stimulus with timing in the nanoseconds. Additionally, an embedded device typically consists of tens to thousands of components interacting with each other. The primary objective of a hardware in the loop (HIL) testbed is to strip away all this complexity and precisely interact with only the desired component. To meet these challenges, this report presents the development of a HIL testbed which not only measures current with a novel analogue feedback circuit capable of reaching a current range of 210 dB, significantly enhancing the precision and sensitivity of measurements while also providing power delivery up to 10A to satisfy inrush currents from FPGAs while simultaneously stimulating and recording data for the embedded DUT.

The HIL testbed comprises three primary modular components: the power profiler module (PPM), the power delivery module (PDM), and the data interposer module (DIM). The PPM employs the novel method for measuring a wide range of currents by a feedback loop of a variable shunt resistance controlled by a cascade of hysteresis analogue circuits. An autonomous high-power mode can additionally halt this hysteresis. This system achieves a current measurement range from 310 pA to 10 A, significantly surpassing the performance of related work [2, 3]. The DUT can supply up to 20 W of power with high accuracy, offering a complete solution for a broad range of embedded device under test (DUT). The DIM enables interaction with multiple devices through the serial peripheral interface (SPI), ensuring reliable communication and isolation between the testbed and the DUT.

#### 1. Introduction

By combining advanced measurement techniques, power delivery capabilities, and data interjection features, this HIL testbed demonstrates a comprehensive solution for testing low-power devices and those requiring high inrush current, such as FPGAs. The modular design of the testbed allows for easy expansion and adaptation to meet the evolving needs of modern embedded systems. It serves as a foundation for future work to integrate this system fully into signal analysis software suites, which could further streamline the testing process and enhance data analysis capabilities.

The remainder of this report is organized as follows: Chapter 2 discusses the related work, providing background on previous research and developments of current measurement, HIL testing and industry devices. Chapter 3 delves into the fundamentals, explaining the concepts and principles necessary to understand the design and implementation of the testbed. In Chapter 4, each module's detailed design and implementation are described, highlighting their key features and performance aspects.

Chapters 5 and 6 focus on the processing system and programmable logic, as well as the simulation of the analogue circuit, which provide essential insights into the current measurements' performance and potential for optimisation. The experimental setup, including the methodology and equipment used in the testing process, is detailed in Chapter 7. Chapter 8 presents the results obtained from the experiments, demonstrating the capabilities and performance of the testbed.

An in-depth discussion of the findings and potential improvements is provided in Chapter 9, followed by a conclusion in Chapter 10 that summarises the key contributions of this work and highlights the potential of the testbed as a foundation for further development in hardware in the loop (HIL) testing for embedded devices.

# Chapter 2

## Related Work

In this chapter, an overview is presented of previous research in the areas of power profiling, power delivery, and sensor emulation. These three topics are of fundamental importance for designing, testing, and evaluating modern electronic systems, particularly in mobile computing and embedded systems.

Since the early days of electronics, it has been crucial to have reliable and reproducible testing environments to verify electronic device performance and functionality. Power profiling, power delivery, and sensor emulation are all essential tools that enable engineers to evaluate the behaviour and characteristics of electronic systems under different conditions.

The following sections review previous work in these areas, highlighting each approach's key contributions and limitations and starting with a discussion of power profiling in chapter 2.1, which involves measuring and analysing the power consumption of electronic systems. In section 2.2, a review of research on sensor emulation is shown, including techniques for simulating sensor output and testing and debugging sensor-based systems. Lastly a general overview of industry devices is given in chapter 2.3.

#### 2.1. Power Profiling Methods

#### 2.1.1. Dual shunt resistor stage

A characterisation of the automatic switch-over of shunts to create a higher dynamic range was given by Pötsch et al. [4], where the authors propose a measurement system for tracking the dynamic power consumption of wireless embedded systems. The system uses a dual shunt resistor stage with an automatic switch-over, which allows for a wide dynamic measurement range of 50 dB (1  $\mu$ A to 100 mA) with an average measurement error of 1.2%. The system also employs two zero-drift current sense amplifiers and a 16-bit SAR ADC for each amplifier, resulting in a higher thermal noise performance and a higher total measurement resolution than a single shunt solution. The measurement system is connected via Ethernet and can forward power samples to a remote computer at a sampling rate of up to 250 kHz.

Using a dual shunt resistor stage and multiple current sense amplifiers allows for a high measurement resolution and low noise performance. The Ethernet connection enables the system to integrate into a remote monitoring setup easily. However, the authors stated that future work is needed to complete the signal processing and communication part. They furthered this work with [5] in the next chapter 2.1.2.

#### 2.1.2. Highly dynamic power consumption measurement

For tracking the highly dynamic power consumption of wireless embedded systems commonly found in IoT devices, the authors of [5] presented a continuation of their previous work [4] on measurement solutions for highly dynamic currents. The system uses a dual shunt resistor stage (100  $\Omega$  and 1  $\Omega$ ) with an automatic switch-over controlled by a Schmitt-trigger, dynamic measurement range from 1  $\mu A$  to several hundreds of milliamps at a ADC resolution of 16 bits. No timing specifications were given on the switching speed. The system can evaluate the timing relation of proprietary RF communication and forecast the expected battery life of a Wifi-based data acquisition system. Above 100 mA both ADCs are in saturation, but the authors achieve coarse current measurement by measuring both the supply voltage and the effective load voltage. [5, p3, eq2]

#### 2.1.3. Shunt Resistor in the loop

A method for estimating the power consumption of peripheral devices while focusing on low development costs in embedded microcontrollers is presented by the authors of Berthou et al. [6]. The method is demonstrated using MSP-EXP430FR5739 nonvolatile RAM and various peripherals on an MSP-EXP430 platform. This allows for measuring all individual peripherals, providing an often overlooked aspect in similar research. A simulator for any instruction set architecture, and peripheral is developed that allows for

#### 2. Related Work

adaptation. The simulator is designed for an MSP-EXP430 platform with an accelerometer, a temperature sensor, and an external radio chip. It achieves an accuracy of 1%in time and 5% in energy consumption estimation, which is more than two orders of magnitude worse than industrial solutions, but the focus was on low development cost.

The main contribution of this work is a simplified power model that enables the accurate simulation of ultra-low power embedded systems using peripherals. The simulation model runs the driver part symbolically by bypassing the whole routine and only simulating its functional effect. The simulator is particularly well-suited for intermittent systems simulation.

#### 2.1.4. Hal Effect Current Sensing

The growing use of linear Hall-effect sensor ICs in open-loop current sensing and measurement applications is shown by Emerald [7]. These sensors offer non-intrusive, safe, and isolated detection of high current levels without dissipating significant power. The applications for these sensors are diverse and continue to expand as designers seek to protect systems, create more reliable equipment, and address safety issues. Current linear Hall-effect sensors have tolerances and temperature drifts that can pose challenges for those designing systems that require single-digit accuracy over a wide range of operating temperatures. The measured voltage from these devices is stated as  $\pm 10$  G. At low currents, this can correspond to  $\pm 50\%$  errors, but at higher currents, with a magnetic field of  $\geq 667$  G, drift is present in the same way, inducing a 1.5% error and indicating a nonlinear relation. This facilitates Hall effect measurements for high current applications. Though future linear sensors may allow for programming after packaging, enabling users to tune the gain, calibrate the output quiescent voltage, and compensate for temperature variations. The authors predict that the opportunities for applying these sensors will continue to expand and multiply as the need for power electronics systems evolves.

#### 2.1.5. Mobile Power Logger for Prototyping IoT Devices

A fully realised hil testbed with a focus on current measurement is shown in Sigrist et al. [3]. In which the authors describe the RocketLogger, a mobile data logger. The RocketLogger combines two circuits, the shunt resistor-based circuit for higher current measurements (max 500 mA) and the feedback ammeter-based circuit for low current measurements (min 5 nA) for a combined range of 165 dB. The switching between these two stages occurs in 1.5  $\mu s$ . It is intended for use in the testing and characterising of energy-harvesting IoT devices, particularly those with ultra-low sleep currents and high communication current requirements. The authors present the RocketLogger's capabilities through a sample energy harvesting application, including its fast and seamless auto-ranging and easy-to-use remote user interface.

#### 2.2. Sensor Emulation and Injection

To thoroughly test a device under test, one needs to be able to simulate the DUT operating conditions and interaction with other devices. In a reproducible test setup, these would not be connected but simulated. This is where the field of sensor emulation and data injection is used.

#### 2.2.1. Automation in HIL Units Development and Integration

The automation of the process of configuring and developing hardware in the loop (HIL) systems is proposed in Brayanov and Eichberger [8]. Their work is able to create and configure HIL simulations on the signal level, and their aim is to reduce the complexity, cost, and setup time required for HIL systems, by using low-cost hardware and a model-based approach for the generation of firmware for distributed HIL systems. The approach generates model based firmware for the HIL,

The authors suggest that this approach has the potential to make HIL systems cheaper, faster, and more widely used, which could lead to faster product development and safer products. However, it is also noted that the approach is limited to signal-level HIL simulation and would require additional formal specification of subsystems and specialized equipment to be applied on the power or mechanics level. Despite these limitations, the proposed approach is considered a good example of the application of formal development methods for the automation of the development process and shift left development."

#### 2.3. Industry Devices

In the final section of this chapter, we will review a selection of commercial devices and tools that are available on the market for power profiling, power delivery, and sensor emulation. These tools are widely used in industry and can serve as helpful reference points for practitioners in these fields. By compiling them here in the table Industry Devices and contrasting these tools with the research approaches discussed in this chapter, we aim to provide a comprehensive overview of the current state of the industry in these areas.

#### 2. Related Work

| Brand  | Digilent           | Dream Source Lab | Nordic               | SALEAE       |

|--------|--------------------|------------------|----------------------|--------------|

| Device | Analog Discovery 2 | DS Scope         | Power Profiler Kit 2 | Logic Pro 16 |

| Inputs                 |             |             |     |                    |

|------------------------|-------------|-------------|-----|--------------------|

| Multi-Use $(A/D/Both)$ | 2 + 16      | 2           | 2+8 | 16                 |

| Input Resistance       | $1 M\Omega$ | $1 M\Omega$ | ?   | 2 MΩ               |

| Input Capacitance      | 16 pF       | 16 pF       | ?   | 10 pF              |

| Input Protection       | $\pm$ 50 V  | $\pm$ 100 V | ?   | $\pm 25 \text{ V}$ |

| Digital                |            |   |                  |              |

|------------------------|------------|---|------------------|--------------|

| Sample Rate (max)      | 100  MS/s  | - | 100  kS/s        | 500  MS/s    |

| Supported Logic Levels | 1.8 to 5 V | - | 1.65  to  5.5  V | 1.2 to 5.5 V |

| Able to stimulate data | Yes        | - | No               | No           |

| Analog                 |                             |                           |                            |             |  |

|------------------------|-----------------------------|---------------------------|----------------------------|-------------|--|

| Sample Rate (max)      | 100  MS/s                   | 1GSa/s                    | ?                          | 50  MS/s    |  |

| Bandwidth (-3dB)       | 9 MHz                       | 100 MHz                   | 50 kHz                     | 5 MHz       |  |

| Max Current            | -                           | -                         | 1A                         |             |  |

| ADC Number of bits     | 14 bits                     | 8 bits                    | 14 bits                    | 12 bits     |  |

| Min/Max Resolution bit | $0.32 \ / \ 3.58 \ { m mV}$ | $0.31 \ / \ 62 \ { m mV}$ | $0.2~/~1000~\mu\mathrm{A}$ |             |  |

| Input Voltage Range    | -25 to 25 V                 | $\pm$ 100 V               | 0.8 to 5.0 V               | -10 to 10 V |  |

| Power Supply  |                |   |              |   |

|---------------|----------------|---|--------------|---|

| Voltage Range | 0.5 to $5.0$ V | - | 0.8 to 5.0 V | - |

| Rated Power   | 2.1 W x2       | - | 5 W          | - |

| Physical  |                   |                                |          |                               |  |

|-----------|-------------------|--------------------------------|----------|-------------------------------|--|

| Size      | $82\ge83\ge22$ mm | $115 \ge 74 \ge 16 \text{ mm}$ | ?        | $92 \ge 92 \ge 15 \text{ mm}$ |  |

| Weight    | ?                 | ?                              | ?        | 220 g                         |  |

| PCB Layer | ?                 | ?                              | 4        | 8                             |  |

| USB Type  | USB 2             | USB 3.0                        | USB 2    | USB 3.0                       |  |

| Price     | 399 \$            | 399 \$                         | 92.50 \$ | 1399 \$                       |  |

Table 2.1.: Summary of related industry devices.

# Chapter 3

### Fundamentals

This chapter is meant as a refresher on the protocols and techniques used to develop the different modules and analogue circuitry.

#### 3.1. Sensing Elements for Current Measurement

Fundamentally the analogue world can be translated to the digital domain with only a few basic parameters to be then analysed with computers. Current needs to be measured for many purposes and functionalities, with only one power usage specification. In literature, as seen in [4], [6], [7] or [3] three main ways of measuring current have crystallized. In the following subchapters, we will have a look at these variants.

#### 3.1.1. Current measurement using Shunt Resistor

A shunt resistor is a low-impedance resistor used to measure a circuit's current flow. Low impedance stands in contrast to the impedance of the circuit the shunt is supposed to evaluate. It is connected in parallel with the load, and the voltage drop across it is measured using a voltmeter. The current flowing through the circuit can then be calculated using Ohm's Law, which states that the current through a conductor between two points is directly proportional to the voltage across those points and inversely proportional to the resistance between them. Shunt resistors are often used in high-precision current measurement applications because they have very low resistance  $R_{Shunt} << R_{Circuit}$ and do not significantly affect the circuit in which they are placed. They can also be used with an amplifier and a display device, such as a digital multimeter or analog to digital converter (ADC), to allow for easy reading and analysis of the measured current.

Lastly, choosing the resistance of the shunt is a tradeoff between the accuracy of the later measurements and a low interference with the device under test (DUT)s circuit.

#### 3.1.2. Measurement using Hall Effect sensor

A Hall-effect sensor is a non-intrusive and isolated detection of high current levels without dissipating significant power. It involves detecting the presence or magnitude of an electric current without interrupting the flow of that current. This is achieved by measuring the magnetic field generated by the current. By analysing the resulting voltage, the current can be determined. One downside of this technique is the interplay between different measurement lines in the same vicinity and the crosstalk seen on one measurement from the state of the other. A last drawback of this technique is the limitation that on high current applications, as seen in the calculations of [1] a 200 A current creates a 13.33 Gauss magnetic field at a distance of 3 cm. This gives an output voltage of 67 mV from the Hall effect sensor. Thus, there are more feasible alternatives for currents ranging in the uA or even nA.

#### 3.1.3. Direct Current Resistance

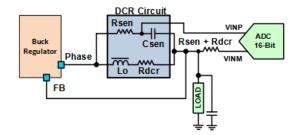

A direct current resistance (DCR) circuit is a space-saving, lossless circuit shown in figure 3.1, which necessitates tuning for proper functioning since it uses the parasitic resistance of an inductor as the current load in contrast to an actual resistance like the shunt. This means further steps must be taken during manufacturing to guarantee the circuit works correctly. The reactive components have a wide range of tolerances which can cause considerable differences in the effective resistance between circuits. Inductors and capacitors have strong temperature dependencies, which can lead to circuit inaccuracies when tuned. The DCR circuit architecture is suitable for measuring gross currents at low supply voltages while maintaining a lossless structure with the lack of components in series with the regulator.

Figure 3.1.: Simple Schematic of a DRC Circuit from [1]

#### 3.2. Hysteric Circuit

Hysteric amplification circuits are electronic circuits that use the phenomenon of hysteresis to output a signal from an OpAmp, depending on the history of the signal. Hysteresis is the property of a system to have a different response to an increasing versus a decreasing input, as visible in figure 3.3. In a hysteresis amplification circuit, the input signal is applied to a control element connected to a feedback loop, such as a transistor or a resistor. The output of the control element is then compared to a reference level with  $R_3$  in schematic 3.2, and the result is used to adjust the gain of the amplifier. One advantage of hysteresis amplification circuits is that they can provide a high degree of linearity and stability over a wide range of input signals. This makes them useful for applications requiring precise amplification and control, such as instrumentation and control systems. Another advantage is that hysteresis amplification circuits can be easily implemented using various technologies, including analogue and digital circuits. This allows them to be used in many applications, from simple signal processing to complex control systems. However, there are also some limitations to hysteresis amplification circuits. One potential drawback is that they require a relatively large amount of power to operate since one connects a supply rail with two resistors to the ground plane while wanting to keep their impedance low enough to create a smaller RC constant and fasterswitching characteristics. This limits their usefulness in portable or battery-powered systems. Additionally, they may be more complex and challenging to design than other types of amplification circuits, with the output being routed back into one input, thus being prone to oscillations.

As per Texas Instruments [9] to calculate the necessary components for the comparator with hysteresis, one should first select the switching thresholds for  $V_{Sense}$  for when the comparator will transition from low to high  $(V_L)$  and high to low  $(V_H)$  visible in figure 3.3. Also, using a sufficiently large  $R_1 \pm 100kOhm$  to minimise the current draw is recommended, although care must be taken not to create too big of a low pass filter. Then the final two resistances become:

$$R_2 = \frac{V_L}{V_{CC} - V_H} \cdot R_1 \tag{3.1}$$

$$R_3 = \frac{V_L}{V_H - V_L} \cdot R_1 \tag{3.2}$$

All of these together create the hysteresis width of  $V_H - V_L$  with all resistances having a  $t_{RX}$  tolerance.

By refactoring this into equation 3.3, one can infer that the tolerances  $t_1$  and  $t_2$  are directly linked to the size of the hysteresis width while  $t_3$  is inversely linked.

$$V_H - V_L = \frac{1}{1 + \frac{t_3 \cdot R_3}{t_1 \cdot R_1} + \frac{t_3 \cdot R_3}{t_2 \cdot R_2}} \cdot V_{CC}$$

(3.3)

Figure 3.2.: Hysteric Circuit

Figure 3.3.: Voltag Plot for Hysteric Circuit

#### 3.3. ADC Precision and Resolution

Analog to digital converter (ADC) convert continuous analogue signals into discrete digital ones. The resolution of an ADC is the tiniest change in analogue voltage that can be detected and converted into a digital value.

The resolution of an ADC is determined by several factors, including the number of bits used in the converter, the reference signal that the input gets compared to, the amplitude of the input signal, and the noise level in the system. A higher number of bits generally leads to better resolution as smaller voltage steps can be measured, increasing the possible digital output values. These possible values get compared to an independent reference voltage.

One way to improve the resolution of an ADC is to use a successive approximation technique by setting a threshold voltage compared to the analogue input signal to determine the digital output value. The threshold is then adjusted based on the result of this comparison, and the process is repeated until the desired resolution is achieved.

Another way to improve ADC resolution is to use oversampling techniques. This involves sampling the input signal at a higher rate than the desired sampling rate. This allows for

averaging over the signals received during one sample period, which reduces noise and gives a more accurate representation of the signal, increasing its resolution.

Finally, ADC resolution can be improved using signal conditioning techniques such as filtering and gain adjustments. These techniques reduce noise and improve the signal-to-noise ratio, thus improving resolution.

The calculation of the actual resolution of an N-bit ADC is

Resolution per bit =

$$\frac{Amplitude}{2^N}$$

(3.4)

#### 3.3.1. Noise in Measurements

Noise in signal lines is a common problem encountered in the context of ADC measurements. Minimising the noise in the measurement line is critical to measure and recording analogue signals accurately.

One common noise source in signal lines is electromagnetic interference (EMI), which can arise from various sources such as other electrical equipment, power supplies, or nearby radio frequency transmitters. EMI can cause unwanted fluctuations in the signal line, leading to inaccurate ADC readings. Another source of noise is thermal noise, which is typically proportional to the square root of the temperature and can therefore be minimised by cooling the measurement equipment or calibrated out by applying a thermal measurement device on

In addition to these noise sources, other factors, such as ground loops where multiple paths to the ground are present for a circuit, resulting in unwanted currents flowing through the measurement circuit, stray capacitances, and switching noise, can also contribute to measurement line noise.

To mitigate these sources of noise, various techniques can be used. Shielding the signal line with a grounded conductive layer can help reduce EMI, while minimising the length of the signal line can reduce its susceptibility to other noise sources. Adding bypass capacitors to the circuit can also help to filter out unwanted noise. Lastly, choosing power delivery components like LDOs instead of bucks reduces the variance in the power supply of the measurement components like the InAmp, drivers or ADCs, since the LDOs output a more stable and noise-free power rail.

#### 3.3.2. Effective number of bits

The effectiveness of an ADC can be measured by its effective number of bits (ENOB). It is defined as the number of bits necessary to achieve a given signal to noise and distortion (SINAD). ENOB is used to quantify the resolution and accuracy of a given ADC, as well as its dynamic range and linearity. The definition most used in literature is [10] equation 1 here eq. 3.5.

$$ENOB = \frac{SINAD - 1.76dB}{6.02} \tag{3.5}$$

To give an example of this with the AD7134 ADC, we use in this project. The ADC is 24-bit and has a SINAD of 106.5 dB in its high-power sampling mode per the datasheet [11]. This would then calculate per eq. 3.5 to a ENOB of 17.4 bits that starkly contrasts with the expected 24 bits. Thus over the entire 4.1 V amplitude that is the reference voltage to the ADC, we only calculated an achievable resolution of 23.7  $\mu$ V per bit step instead of the originally expected 0.24  $\mu$ V per bit when one contrasts the 17.4 bits versus the initially expected 24 bits.

# Chapter 4

## Design Implementation Of Modules

In this chapter, we dive into implementing and designing the crucial modules responsible for creating this hardware in the loop (HIL) test environment. The chapter covers the design and implementation details of the power profiler module (PPM), power delivery module (PDM) and data interposer module (DIM) designed for this thesis and additionally the FPGA SoC Module integrated into this work. A particular emphasis will be given to addressing the most significant challenge faced in the power profiler module: the hysteric cascade that drives the shunt resistor for dynamic range current measurement and the corresponding high power mode that pauses this cascade.

#### 4.1. Modularity

We employ a PCIe X1 connector from the compute board to the different modules to guarantee modularity and the ability to support future modules. For this proof of concept, we only have one connector per module. Still, the choice of FPGA and power delivery is designed to sustain multiple measurement, delivery and interposer modules for future versions, with the FPGA's ability to reroute all I/Os to accommodate not yet designed functions and modules.

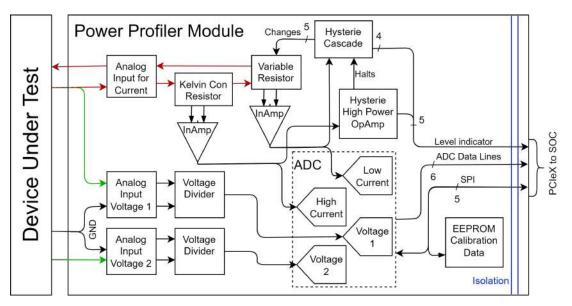

#### 4.2. Power Profiler Module

The power profiler module (PPM) represents the novel work of this thesis. As visible in the block diagram, the PPM 4.1 employs a combination of hysteresis circuits chained (cascaded) together to control the shunt resistance used for current measurements. A novel way of combining this low current measurement is implemented with another kelvin-connected shunt for higher currents. Its hysteresis circuit can halt the

low current cascaded circuits and short the shunts not to increase voltage drop over the measurement circuit. Additionally, two voltage measurement terminals are implemented. These four terminals output the voltage into a driver /ADC combination for four data channels. An EEPROM is on the module to store module identification and calibration data.

Figure 4.1.: High Level Block diagram of PPM Data and Measurement Lines

Figure 4.2.: Power Profiler Module

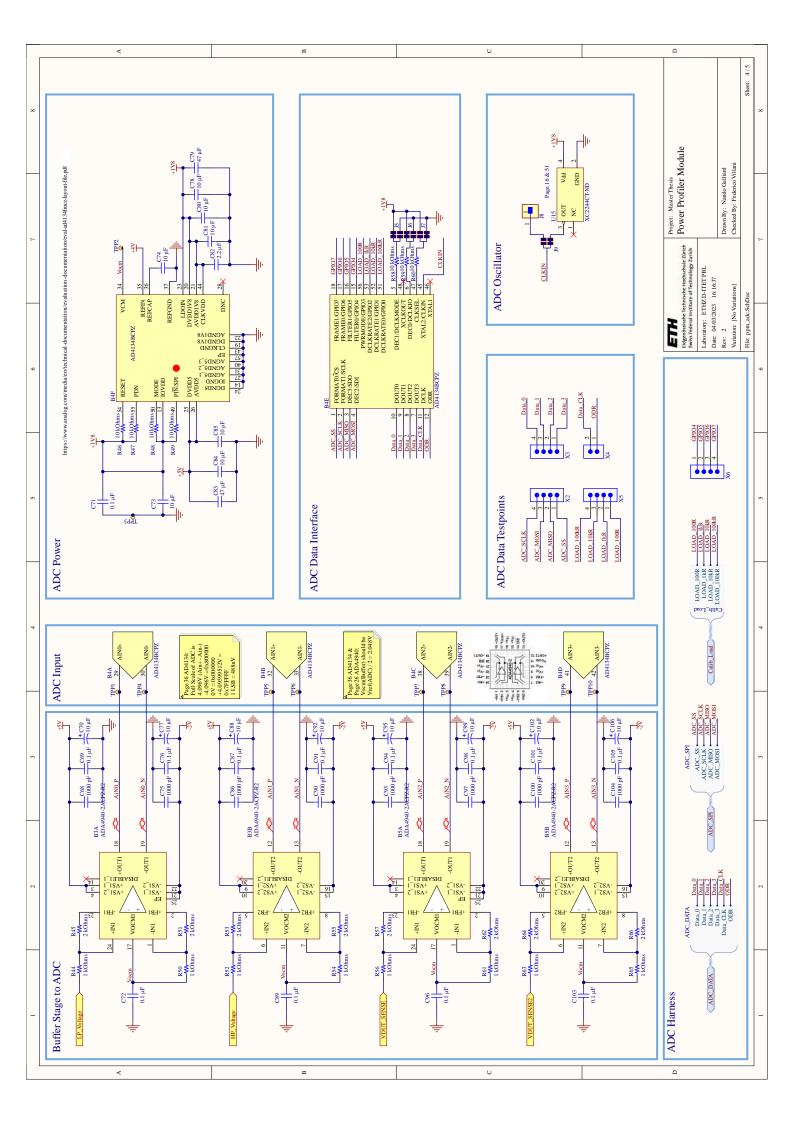

#### 4.2.1. ADC AD7134

The AD7134 [11] is a quad-channel analog to digital converter (ADC) offering highdensity multi-channel data acquisition in a small form factor. The ADC has an integrated asynchronous sample rate converter that supports a wide range of output data rates and digital filter profiles, including options for frequency domain analysis, low latency time domain analysis, and optimal noise performance. The ADC also supports on-board averaging for improved dynamic range and offers two device configuration schemes, SPI and pin control mode. With our implementation, the system uses a 5V source voltage and has a 4.096V reference voltage with a common mode voltage of 2.048V. It employs four separate ADC converters that aren't interconnected, and the data is output on six serialisation lines to the FPGA. The ADC runs with a CMOS-given clock of 48 MHz and can output 1.5 MS/s in low power mode and 374 kS/s in high performance mode we use. In appendix A.2 table A.1 are all SPI reprogrammed registers that differ from the reset values.

This analog to digital converter was chosen since it has a high 107.21 dB dynamic range and RMS Noise of  $12.\mu$ V at 374 kS/s and four different measurement channels.

#### 4.2.2. Instrumentation Amplyfier

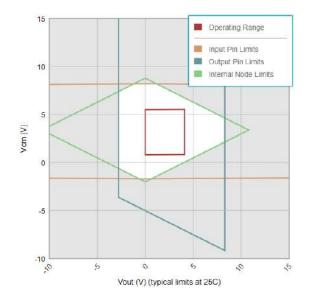

We employed the AD8421ARZ, an instrumentation amplifier from Analog Devices [12] to amplify the voltage drop over the shunt resistor. Its high CMRR of 120 dB allows for an accurate and steady amplification, even when the input signals vary over time. Its low offset voltage of 60  $\mu$ V minimises drift and temperature-related errors. Furthermore, the amplifier has a low input bias current of 500 pA.

Due to other constraints in the system, the amplifier will receive a maximum voltage of 50 mV. Therefore, to measure in the full amplitude range of the ADC at 4.1V, an amplification of  $4.1V \div 0.05V = 82$  is necessary, which is achieved with an external resistor of 122 Ohm. At this amplification, the settling time to 0.0001% is 0.5  $\mu$ s and the bandwidth three MHz and thus not a significant source of error compared to the MOSFET slew time or the ADC sampling rate.

To sample the entire voltage range of 0.8V to 5.5V, a positive supply of 10V and negative rail of -4V was desired, finally leading to the diamond plot in figure 4.3 of our instrumentation amplifier.

Figure 4.3.: Diamond Plot of AD8421ARZ under design specifications

#### 4.2.3. Driver Input to ADC

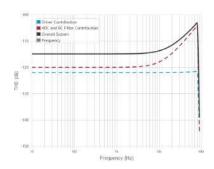

The accuracy and precision of the ADC rely heavily on the proper biasing of the input voltage. The ADA4940, a high-performance operational amplifier, is designed to provide the necessary drive to precisely push both positive and negative input voltages to the ADC. The driver is operated in inverting mode with 2V/V gain to transform the 4.1 V input into  $\pm 4.1V$ . The absolute maximum performance of the AD7134 is set at 374kSps in high performance, and with the other settings mentioned in chapter 4.2.1, we thus get a maximum input frequency that is allowed at 1/2 of this at 187 kHz. At these frequencies of the ADC and driver system, the noise and distortion values can be seen in table 4.4 and the contribution of the system total harmonic distortion (THD) over all frequencies can be seen in figure 4.5

| Noise and Distortion at 187 kHz |            |  |  |  |  |

|---------------------------------|------------|--|--|--|--|

| Parameter                       | Value      |  |  |  |  |

| THD                             | -139 dB    |  |  |  |  |

| ENOB                            | 17.3 bits  |  |  |  |  |

| SINAD                           | 106 dB     |  |  |  |  |

| SNR                             | 106 dB     |  |  |  |  |

| System Noise                    | 14.6 uVrms |  |  |  |  |

Figure 4.4.: N&D Summary

Figure 4.5.: Contributions to System THD

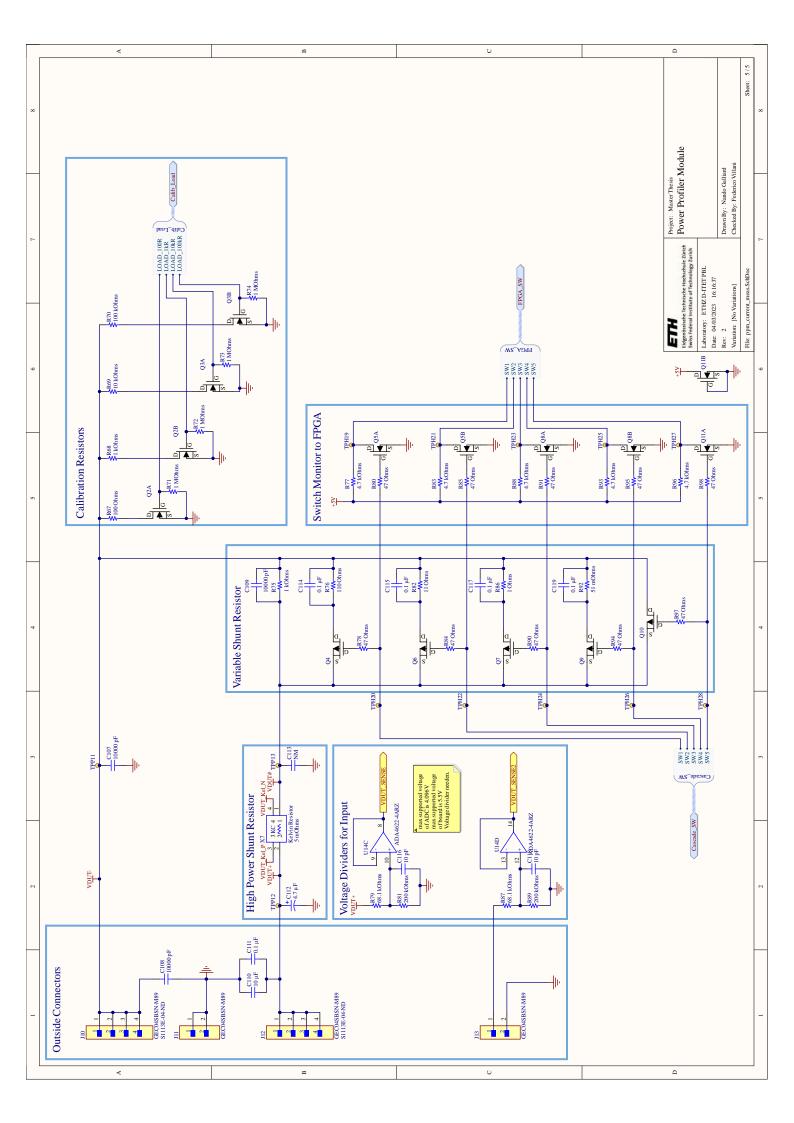

#### 4.2.4. Variable Shunt Resistor

Using a shunt resistor is inherently limited by the resistance  $R_S$  that one can reliably create with the presence of trace resistances and other components in the circuit. The MOSFETs we use to engage the variable shunt resistor are by design inside of the circuit sector that the voltage drop is measured from as visible in figure 4.6, and thus their drain to source resistance  $R_S D$  needs to be accounted for.  $R_S D$  is highly temperature dependent and at room temperature the MOSFETs we use already have a  $R_S D$  of (  $11 \pm 4$ ) $m\Omega$ .

Thus  $R_S >> R_S D + R_{Trace}$  for this setup to reliably create the expected voltage drop. The shunt resistances in total for our design are limited to equal about 50  $m\Omega$  to anticipate the created voltage drop still correctly. This number can be determined by looking at the inherent resistance  $R_S D$  of the MOSFETs and their temperature-dependent variability. With the error propagation equation 7.1, one can arrive at  $61\pm4.03m\Omega$  resistance, which is already a 6% variability. For this prototype, we decided on one magnitude step per resistor. Find the desired resistance values and the corresponding resistances that are needed to create this parallel resistance in table 4.1 with the resulting current ceiling if the desired voltage drop of 50 mV is to be maintained.

| Desired Resistance | Installed R  |           | Current $\uparrow$ |         | Current $\Downarrow$ |         |

|--------------------|--------------|-----------|--------------------|---------|----------------------|---------|

| 1000 Ω             | $1000\Omega$ | $\pm 1\%$ | 50                 | $\mu A$ | -                    |         |

| 100 Ω              | $111\Omega$  | $\pm 1\%$ | 500                | $\mu A$ | 378                  | $\mu A$ |

| $10 \ \Omega$      | $11\Omega$   | $\pm 1\%$ | 5.046              | mA      | 3.783                | mA      |

| 1 Ω                | $1\Omega$    | $\pm 1\%$ | 55.046             | mA      | 38.147               | mA      |

| $50 m\Omega$       | $51m\Omega$  | $\pm 1\%$ | 1.035              | A       | 342.511              | mA      |

| $5m\Omega$         | $m\Omega$    | $\pm 1\%$ | -                  |         | 342.511              | mA      |

Table 4.1.: Variable Shunt Resistor Resistances

Figure 4.6.: Variable Shunt Resistance Schematic

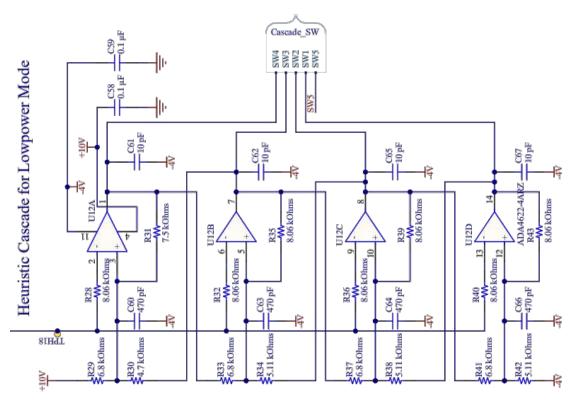

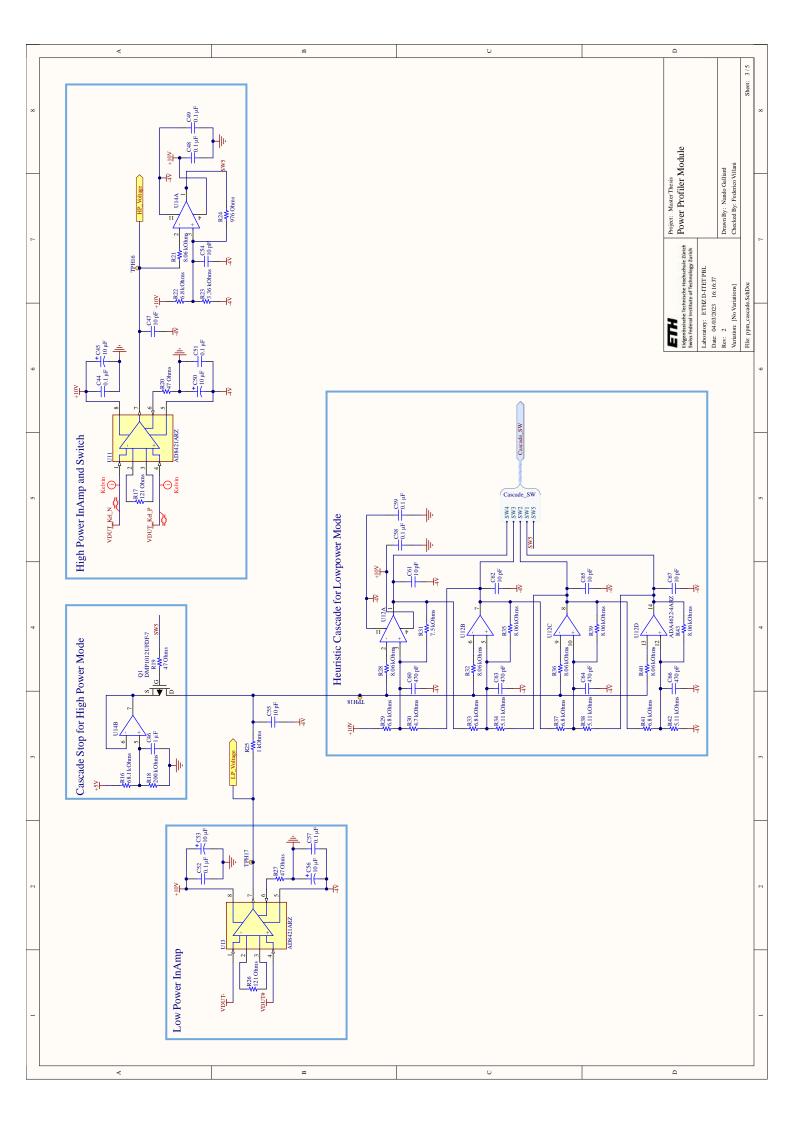

#### 4.2.5. Hysteresis Cascade

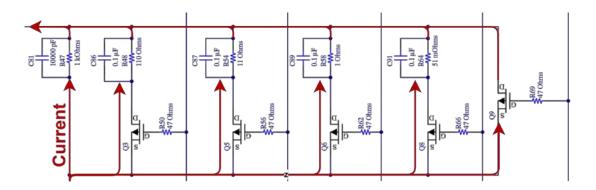

To engage these variable shunt resistors, we employ multiple hysteric opamps in series that use the instrumentation amplifier as input  $V_{Sense}$  (TPH18), as visible in figure 4.7. This has the voltage drop over the shunt as input, so care must be taken not to create oscillations. On the other hand, this creates a fast analogue circuit only majorly constrained by the RC low pass filter created by the InAmp. At InAmp state 0 V, all outputs 1,7,8 and 14 are high of the OpAmps and thus, only U12D has a + input of about 2 V because of the voltage divider made up of  $R_{41}$  and  $R_{42}$  while the other three are at 10 V. Thus U12D is the first to react to a change over  $V_H$  from  $V_{Sense}$ . Output 14 falls to the negative supply rail of -4 V, and with that, U12C from switch two is primed with the voltage divider. A state change can happen if  $V_{Sense}$  falls below  $V_L$  of U12D or rises above  $V_H$  of U12C. These state changes are accompanied by changes in the shunt resistance and  $V_{Sense}$ .

Figure 4.7.: Hysteresis Cascade Circuit Schematic

In chapter 3.2, we introduced equations 3.1 and 3.2 for the calculation of the resistances in one hysteric circuit. Now we want to dimension the falling Voltage  $V_L$  of the circuit in comparison to the rising Voltage  $V_H$  of the previous circuit. We introduce an arbitrary tolerance 1-t of 2% to the voltage level to minimise oscillation. The following calculations

are dependent on the in stage X currently engaged shunt resistor  $R_{SX}$ ,  $V_{HX}$ ,  $V_{LX+1}$  and the corresponding tolerances  $T_C$  of the real world components used. We used 1% tolerance components for all resistances and the worst-case tolerance for the calculations. Using the worst case lets us dimension the hysteresis steps in a way that even with the most disadvantageous distribution, we do not create unnecessary oscillations. Equal in both scenarios are the currents  $I_X$  and  $t \cdot I_{X+1}$  flowing in both stages with the difference of the introduced tolerance t. After the usual conversions, we end with equation 4.3 that allows us to dimension the falling Voltage  $V_L$  for each stage.

$$I_X = t \cdot I_{X+1} \tag{4.1}$$

$$\frac{V_{LX+1}}{T_{R_{SX+1}} \cdot R_{SX+1}} = t \cdot \frac{V_{HX}}{T_{R_{SX}} \cdot R_{SX}}$$

(4.2)

$$V_{LX+1} = t \cdot \frac{T_{R_{SX+1}}}{T_{R_{SX}}} \cdot V_{HX} \cdot \frac{R_{SX+1}}{R_{SX}}$$

$$\tag{4.3}$$

With these calculations, the maximum ADC voltage range of 4.096 V that is defined as the  $V_H$  of the hysteresis, a  $R_1$  chosen to be 6.8 kOhm and the desired shunt resistances determined in chapter 4.2.4, we can now determine the ideal makeup of the hysteric amplification cascade. As discussed in chapter 3.2 with the worst-case swing of the tolerances and resistances available on the market, the final makeup of the cascade looks as seen in table 4.8. These calculations have been programmed in a helper script **cascade** helper.ipynb in the Spice project repository.

| Stage | $V_L$   | tol             | $V_H - V_L$ | ideal $R_2$   | ideal $R_3$     | final $R_2$     | final $R_3$     | tol        |

|-------|---------|-----------------|-------------|---------------|-----------------|-----------------|-----------------|------------|

| 1     | 0.401 V | $\pm$ 1.48 $\%$ | 3.695 V     | 5068 $\Omega$ | $8099 \ \Omega$ | 5100 $\Omega$   | $8060 \ \Omega$ | $\pm 1 \%$ |

| 2     | 0.398 V | $\pm$ 1.48 $\%$ | 3.698 V     | 5065 $\Omega$ | $8087~\Omega$   | 5100 $\Omega$   | $8060 \ \Omega$ | $\pm 1 \%$ |

| 3     | 0.368 V | $\pm$ 1.48 $\%$ | 3.728 V     | 5030 $\Omega$ | 7966 $\Omega$   | 5100 $\Omega$   | $8060 \ \Omega$ | $\pm 1 \%$ |

| 4     | 0.212 V | $\pm$ 1.48 $\%$ | 3.884 V     | $4851~\Omega$ | 7374 $\Omega$   | $4700 \ \Omega$ | 7500 $\Omega$   | $\pm 1 \%$ |

Figure 4.8.: Cascade Components

Figure 4.9.: High Power Mode for Current Measurement

#### 4.2.6. High Power Mode for Current Measurement

As described in chapter 4.2.4 the intrinsic resistance variability of the MOSFETs necessitates a workaround if one wants to measure higher currents while still keeping the variable shunt resistor design approach. We approached this in a novel way. We connected a small kelvin-connected shunt resistance in series to the variable shunt resistances. This shunt resistance is visible in figure 4.9. We need a secondary dedicated instrumentation amplifier (InAmp) and ADC to capture the resulting voltage. However, this approach is instrumental because it removes the MOSFET from the calculation altogether. As a result, we can easily measure a far more extensive current range without compromising on the high resolution of the lower currents. To avoid influencing the DUT circuit with a higher voltage drop than intended, removing the variable shunt from the testing circuit is necessary. We designed this functionality by having a parallel trace to the shunt that can be shortened with another MOSFET. This, though, would let the  $V_{Sense}$  fall to zero and with it, the cascade steps to the lowest level. So after disengaging the high power mode, the whole cascade would need to stabilise again, increasing the unusable data window from one step switch to four. Thus the also hysteric opamp of the HP mode enables a steady 4V source to the cascade input  $V_{Sense}$  to halt the cascade at switch four.

#### 4.2.7. Power Planes

While multiple power planes are necessary for the module's functionality, a highlight needs to be set on the planes that supply the hysteric cascade, instrumentation amplifier and ADC since these need to be as removed from noise as possible. For this purpose, the general path was to convert the 12 V input from the isolator to the corresponding power planes with buck converters while introducing a Low-dropout regulator (LDO) before the measurement devices that clean the rail from any introduced noise from the supply or

buck. This intermediate step is necessary since, for example, when one would only use a LDO to convert a 12 V rail down to a 1.8 V rail with 200 mA of load current, this would create 2.18W of power dissipation on the area of a small coin or roughly equivalent to the heating output of a typical electronic stovetop scaled for the same area.

| Plane            | Current Density | Supply Target | Supplies                  |

|------------------|-----------------|---------------|---------------------------|

| 10 V             | 56  mA          | 100  mA       | Cascade, OpAmp            |

| $5 \mathrm{V}$   | 62  mA          | 100  mA       | Driver, Isolation, EEPROM |

| $4.096 {\rm V}$  | -               | -             | ADC                       |

| $1.8 \mathrm{V}$ | 200  mA         | 300  mA       | ADC, Isolation            |

| GND              | -               | -             | ALL                       |

| -2 V             | -               | -             | Driver                    |

| -4 V             | -               | -             | Cascade, OpAmp            |

| -5 V             | -               | -             | -2 V,-4 V LDO             |

Table 4.2.: Current Density on PPM

#### 4.2.8. Isolation

Isolation is very important on a measurement device to mitigate power supply noise interfering with the measurements and also to keep any components safe from any electro static discharge (ESD) that might occur in either direction. Multiple isolation components are necessary to deliver power and send independent data over an isolation barrier. For generic data signals, we employ the ISO6760 [13] for high-speed independent data, and for timing critical data like SPI, we use the ADUM3150 [14] isolator specifically designed for the protocol and 4 secondary devices addressable by one secondary select line with an additional two-wire mux.

Since we filter the power planes again after the isolation, the power isolator didn't need to be measurement grade and needed to have enough throughput. Thus we went with the PYBJ6 [15].

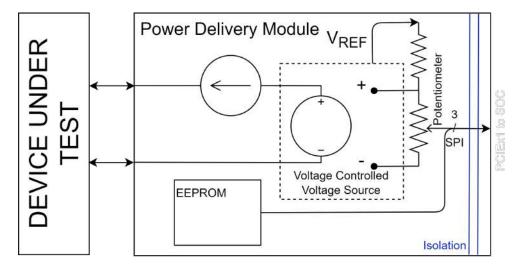

#### 4.3. Power Delivery Module

Figure 4.10.: Block Diagram of PDM

The power delivery module (PDM) represents a necessary step in sustaining a device under test environment even though it is not the driving focus of this thesis. The ability to sustain the most common power needs that a DUT in the embedded system world could have guided the design of this module. We can accommodate the range of 0.86 to 5.5 V with a max of 20 W or 10 A.

#### 4.3.1. DC-DC Power Delivery to DUT

For the power delivery to a DUT, we employed the ATA010 by GE that could variably deliver the power needs, but without incorporating a current limiter which was left for future implementations. This module output voltage is set with an external resistance that can be changed at runtime. Thus the potentiometer AD5270 was introduced to the module, which entails 100  $k\Omega$  over a variability of 1024 settings creating a high accuracy desired output voltages. Only the range between 0.75 V and 0.86 V can not be set in this implementation since the resistance can not be set high enough to program the output to lower than 0.86 V. The test results for this setup are visible in chapter 8.5.

#### 4.3.2. Isolation

Although the same isolators were used for data transfer as described in chapter 4.2.8, the power delivery modules required additional filtering to ensure (electromagnetic compatibility (EMC)) due to the high amount of power they could draw. This entailed a fuse and sufficiently large inductance coil visible in figure 4.11, which is also why the power delivery system for the module makes up over half of the area. Lastly, sufficient power delivery needed to be guaranteed so that the DUT could deliver up to at least 20 W of power as per the initial requirements definition of this system. Thus we installed a 30 W DC/DC isolator [16] to power the rest of the module sufficiently.

Figure 4.11.: High-Level Block Diagram of PDM Data and Power Delivery Lines

## 4.4. Data Interposer Module

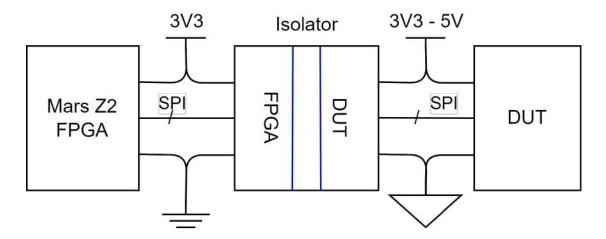

At the initial stages of this thesis, a third module was planned. Still, after further feature definition, the use for version one of this module was only targeted at being able to interact with the DUT over an SPI bus as shown in figure 4.12. Thus this module was incorporated into the interposer board that connects FPGA SoC with the initial power plug and the different modules. The same SPI isolator was used to create this feature to get the necessary isolation of the DUT. Though with the shortcoming that the DUT needs to deliver the power to the isolator itself. This furthers the strain on the DUT with an additional 13.5 mA at peak frequency, but we deemed it acceptable for the first proof of concept before developing a dedicated module. The main can interact with up to four second devices on a single SPI line up to a data rate of 34 Mb/s.

Figure 4.12.: Measurement Setup data exchange with DUT

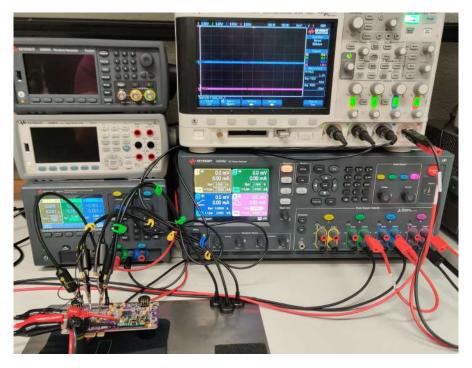

# 4.5. Mars ZX2 Module

For running the prototype's firmware and real-time operating system, we used the Mars ZX2 SoC module by Enclustra. The Mars ZX2 System-on-Chip (SoC) module is an embedded processing system that utilises the Xilinx Zynq-7010 All Programmable SoC device. The module incorporates fast DDR3L SDRAM, quad SPI flash, a Gigabit Ethernet PHY, USB 2.0 On-The-Go PHY, and a real-time clock. It also contains an ARM chip and a field programmable gate array (FPGA) that allows for flexible development and high-performance data processing.

This module is designed in a small SO-DIMM form factor, which allows for space-saving hardware designs and easy integration into the target application, thus sing the Mars ZX2 SoC module can greatly reduce development effort and redesign risk when compared to building a custom SoC hardware.

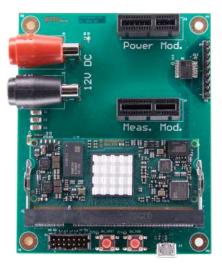

Figure 4.13.: Data Interposer Module

# Chapter 5

# Processing System and Programmable Logic

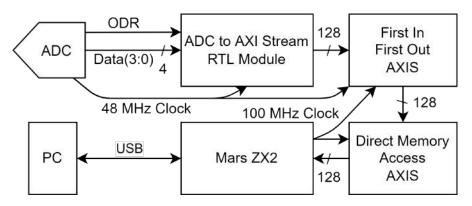

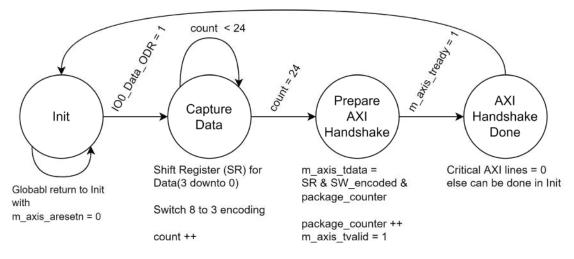

Separating the processing system (PS) and programmable logic (PL) allows for offloading specific processing tasks to the programmable logic, which can be optimised for specific operations. This can increase the system's overall performance and make it more efficient with the possibility also to implement advanced features and functions, such as parallel processing and hardware acceleration, which can further enhance the system's capabilities. As visible in figure 5.1, the data stream from the ADC gets handled by a register transfer level (RTL) module in PL that handles the data packaging further discussed in chapter 5.1. Still in PL is a FIFO for data buffering between clock domains and a direct memory access (DMA) module to save the data to the PS memory without halting the processing core operations.

Figure 5.1.: Real Time Datastream from ADC to PC

5. Processing System and Programmable Logic

Figure 5.2.: State Machine of ADC RTL Module

Figure 5.3.: 128-bit AXI Stream Package

## 5.1. ADC RTL Architecture

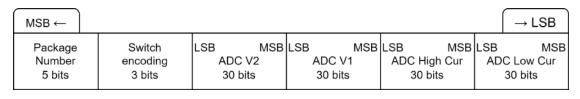

To better streamline the data gathering process that arrives from the ADC and be able to implement the data stream into existing programmable logic (PL) protocols, we wrote a register transfer level (RTL) module that takes the ADC clock, output data rate (ODR) and four data lines with the cascade switch signals and combines them to one 128 bit encoded package visible in figure 5.3. Figure 5.2 shows the state machine of this module.

Of note for this model is the AXI Stream, the standard interface to exchange data for Xilinx intellectual property (IP)s. This protocol employs a main and second relationship between two participating IPs with a valid and ready signal for a handshake. This behaviour was also implemented into the state machine, and these AXIS signals are visible with the designation m\_axis since the module takes the role of main for the exchange.

# Chapter 6

# Simulation of Analog Circuit

As seen in chapter 4, the whole measurement setup is composed of a variable shunt resistor that is engaged by a hysteric amplification cascade and a high power mode to engage an additional in-series Shunt. The goal of this chapter is the comprehensive simulation and analysis of the critical analogue circuitry for the power profiler module (PPM).

## 6.1. Simulation Software

The simulations were done with advanced design systems (ADS) from Keysight, a software platform for electronic design automation (EDA). It provides a comprehensive suite of tools for designing and simulating radio frequency (RF), microwave, and high-speed digital circuits. ADS offers a range of features, including schematic capture, simulation, and layout, to help streamline the design process.

### 6.2. Simulation Settings

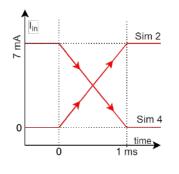

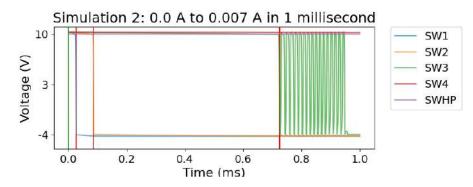

The simulation was done with a full recreation on the significant analogue circuitry of the power profiler module (PPM) and the official spice models for components like the instrumentation amplifier, the MOSFETs or, for instance, with the OpAmp the corresponding values were extracted from the datasheet. With these simulations, some possible changes in components to the implemented prototype will be highlighted and touched upon in the discussion chapter 9 to put some focus on design challenges and tradeoffs. The simulations which do not correspond to the current PPM version will be marked in the title with  $\simeq$ . Figures 6.1 and 6.2 correspond to a rising or falling current and to the step measurement that was flowing through the shunt resistance.

#### 6. Simulation of Analog Circuit

Figure 6.1.: Rising and Falling Currents

Figure 6.2.: Step Function Currents

### 6.2.1. Rising Current 0A to 7 mA

In the zero to 7 mA operating range, one can see some oscillations in the state transition when switch three engages. Chapter 6.2.2 explores another design approach to diminish these oscillations. This behaviour will be further explored in chapter 9.1, and the measurement setup is further discussed in chapter 7.2.

# 6.2.2. Rising Current 0A to 7 mA $\simeq$ Bigger Resistor at MOSFET Gate

With the choice of one single MOSFET type for every current field comes a tradeoff. For smaller currents, these MOSFETs have too prominent of channel width and are thus switching slower, which creates an oscillation in the lower current fields. This could be improved or even remedied with an increase in the in-series resistance to the MOSFET gates, creating a more significant RC time constant that slows the switching behaviour. This behaviour is simulated here by increasing this resistance by one magnitude.

#### 6.2.3. Falling 7mA to 0A

In the reversed current trend direction, these oscillations are not visible, yet an overcorrection of switch one is visible when switch two rose to a voltage high level.

#### 6.2.4. Rising Current 0A to 1.1A

For higher currents, this behaviour is not visible. On the other hand, the high power mode switch engages quite slowly in 0.1 ms compared to the expected  $\mu s$  switching range of the MOSFET. This behaviour could not be replicated in the prototype, and the device switches as expected, as seen in chapter 8.2.

#### 6.2.5. Falling Current 1.1A to 0A

The reverse trend simulation shows the same slow rise time of the high-power switch five. No further oscillations take place.

#### 6. Simulation of Analog Circuit

#### 6.2.6. Switching time of Cascade Steps

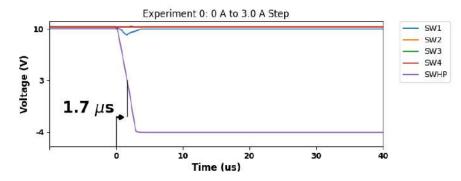

To simulate how fast the cascade can switch, a step function current was applied to the shunt resistance with a rise time of 1 ns. The step function of simulation experiment one was enough to trigger the high-power mode. In figure 6.3, one can thus see the high power mode engage almost instantly and halting the cascade in its current state with an engaging time of 1.7  $\mu s$ .

When only enough current was applied to fully traverse the low-power mode as seen in figure 6.4, the cascade took 11.6  $\mu s$  for all four stages, thus switching each step in 2.9  $\mu s$ .

Figure 6.3.: Step Current Through Shunt at 3 A

Figure 6.4.: Step Current Through Shunt at 800 mA

## | Chapter

# Experimental Setup

In this chapter, the setup of all experiments is introduced with the definition of the ground truth corresponding voltage and current levels. If a file in this chapter is named and not explicitly told otherwise, one can find it in the enclosed git in the appendix D.

# 7.1. Definition Of Ground Truth

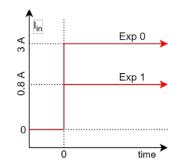

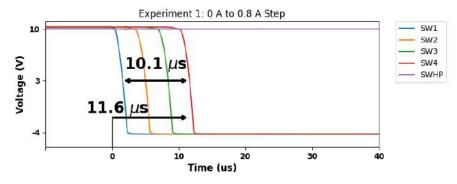

To create a reproducible and synchronizable ground truth, we employ the N6705 DC power analyzer by Keysight. This device can, on four different outputs in free or coupled mode, manage voltage up to 6 V and current load up to 3 A with variable slew and timing. For the experiments pertaining to the cascade, 3 A suffices to trigger all cascade steps and activate the high-power mode. One of the outputs can thus be set to send an arbitrary pulse coupled with the beginning of the current output and thus act as a trigger for any other devices in the test.

To measure the voltage level of the cascade steps and the buffer output we use an oscilloscope Agilent Tech. MSOX-X 3014A with the aforementioned trigger signal that is further touched upon int able 7.1 To get all five switches, we thus did two runs of this experiment and merged the data corresponding to the trigger.

| Oscilloscope          | Agilent Tech. MSO-X 3014A (4-Kanal, 100MHz, $4GS/s$ )                 |

|-----------------------|-----------------------------------------------------------------------|

|                       | Impedance: $1M\Omega$ on all measurements, if not specified otherwise |

| Voltage Source        | Keysight N6704 (Duty Cycle 100%,                                      |

|                       | Waveform DC 6.12 V, Output High Z Termination,                        |

| Current Source        | Keysight N6704 (Output High Z Termination,                            |

|                       | Waveform Exponential Rise and Fall Triangle 0A to 3A to 0A,           |

| Signal generator      | Keysight N6704 (Rectangular waveform generator, 1 kHz)                |

| PCB Probe             | PCBite SP200, length: 80 cm, attenuation 10:1                         |

| Coaxial cable         | RG58 with BNC connector, length: ca. 1m, attenuation 10:1             |

| DC-Voltagesource FPGA | Output Votlage 12V, Output Current max 5A, 60W                        |

Table 7.1.: Devices used for Measurements

## 7.1.1. Measurement Uncertainties

Due to the inherent inaccuracies of the sensors and components used in measurement systems, it is common to encounter various sources of error that can significantly affect the accuracy of measurements. These sources of error can arise due to a variety of factors, such as measurement noise, drift, and non-linearity, among others.

Due to these inaccuracies, we see the following sources of error in table 7.2 have an influence on measurement accuracy.

| Source of Error             | Relative Value                              | Absolute Value                                   |

|-----------------------------|---------------------------------------------|--------------------------------------------------|

| Capacitive measuring ca-    | 80 cm length                                | 18 pF                                            |

| ble PCB                     |                                             |                                                  |

| Capacitive measuring ca-    | 1m length, 100 pF/m $$                      | 100 pF                                           |

| ble else                    |                                             |                                                  |

| Oscilloscope Vertical Reso- | 8 Bits: Measuring range of                  | $(V_{Max} - V_{Min})/256$                        |

| lution                      | $2^8 = 256$ possible states                 |                                                  |

| Oscilloscope Vertical Gain  | $\pm$ 3% full scale ( $\geq$ 10             | $8 \text{ houses} \cdot V/\text{div} \cdot 0.03$ |

| Accuracy                    | $\mathrm{mV/div})$                          |                                                  |

| Oscilloscope DC Vertical    | $25 \text{ ppm} \pm 5 \text{ ppm}$ per year | Negligible                                       |

| Accuracy                    | (ageing)                                    |                                                  |

| Oscilloscope Horizontal     | 12 Bits with $\geq 20\mu s/dec$ :           | $(t_{Max} - t_{Min})/4096$                       |

| Resolution                  | Measuring range of $2^{12} =$               |                                                  |

|                             | 4096 possible states                        |                                                  |

| Internal Resistance Oscil-  | Leakage Current through                     | Negligible                                       |

| loscope                     | Internal Resistance                         |                                                  |

Table 7.2.: Single Measurement Errors

For the general measurement Y, one can use the gaussian law of error propagation 7.1 to calculate the error  $\Delta Y$  of this measurement in dependency of all uncertainties. And following this, the equations 7.2 to 7.4 summarise the measurement uncertainties used in the following experiments.

$$\Delta Y = \sum_{j=1}^{k} \left(\frac{\delta f}{\delta x_j} \Delta x_j\right) \tag{7.1}$$

$\Delta U =$ Vertikal Resolution + Vertikal Gain Accuracy of the oscilloscope (7.2)

$$\Delta I = \sqrt{\left(\frac{\Delta U}{R}\right)^2 + \left(-\frac{U}{R^2}\Delta R\right)^2} \tag{7.3}$$

$$\Delta \phi = \text{Time base accuracy} \tag{7.4}$$

- The DC voltage source (GW Instek GPS-3303S) has a measurement uncertainty of less than ±0.03% (k=2). The DC voltage source may be operated with a maximum of +18 V DC for reasons of protection for the circuit. This results in an error of ±6 mV. So even if the measurement uncertainty is ±0.03%, the error would still be negligible. The DC voltage source is therefore assumed to be constant.

- The values of the components (resistors, capacitors) are only used for theoretical calculations. Therefore, the tolerances listed in chapter 4.2.4 do not play a role for the measurement uncertainty in voltage measurements.